개요

이렇게 정리하는 이유는 업무상 할당 받은 MAC과 PHY 칩 둘 사이에 사용되는 인터페이스를 확인할 필요가 있었다(이미 기존에 포팅은 완료된 상태). 기존 포팅된 소스를 확인해보니 두 칩 사이에 SGMII라는 인터페이스를 활용 중이였고 회로도 상에서도 SGMII를 위한 여러 핀들이 이미 할당되어 있었다.

나의 대학원 때의 주된 연구는 대부분 상위 레이어 중심으로 했기 때문에 하위 레이어의 지식은 거의 무지한 상태였어서 MII 인터페이스가 어떠한 용도인지 몰랐으며 MII의 상위 버전인 SGMII에 대해서도 잘 알지 못했다. 그래서 간단히 이렇게라도 정리해보며 공부를 해보았다.

따라서, 본 문서에서는 MII에서 SGMII까지 간략히 살펴보기로 한다.

예전 10/100Mbps의 성능의 이더넷 칩에는 MAC과 PHY가 하나의 칩에 내장되어 있었다고 한다.

하지만, Gigabit(1000Mbps 이상) 이더넷이 되면서 MAC과 PHY가 분리되어 동작하게 되었다.

MAC은 순수한 디지털 데이터를 처리하며,

PHY는 아날로그 신호를 1과 0의 디지털 데이터로 변환하는 역할을 한다.

PHY는 OSI 7계층에서 가장 하단의 1계층에 위치하며, MAC은 PHY의 위의 계층인 2계층에 위치한다.

여기서 MII는 IEEE 802.3u 표준 인터페이스로 PHY와 MAC 계층 사이에 위치하는 인터페이스이다.

MII를 사용한다면, PHY가 변해도 MAC은 바뀌지 않아도 된다.(당연히 Layer 구조이니깐..ㅎ)

MII는 현재 속도를 높이고 신호선을 줄인 다음과 같은 다양한 버전들이 존재한다.

- MII(Media Independent Interface)

- RMII(Reduced MII)

- GMII(Gigabit MII)

- RGMII(Reduced Gigabit MII)

- SMII(Serial MII)

- SGMII(Serial Gigabit MII)

- HSGMII(High Serial Gigabit MII)

- QSGMII(Quad Serial Gigabit MII)

- XGMII(10-Gigabit MII)

MII : Media Independent Interface

MII는 가장 초기에 개발된 MAC, PHY 인터페이스이다.

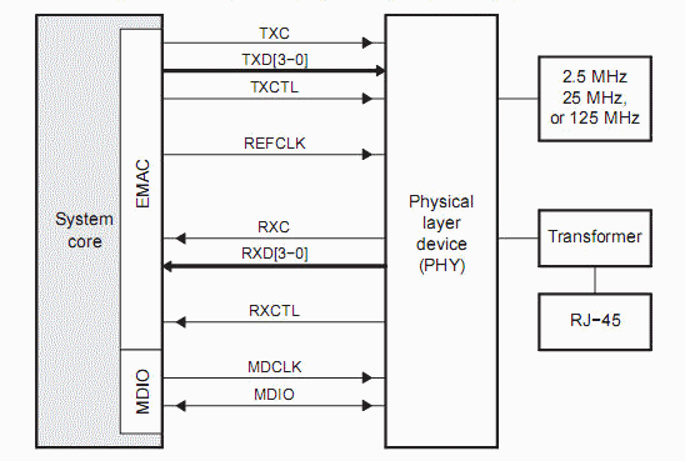

TXD[0...3], RXD[0...3], REF_CLK, TX_EN, CRS, MDIO, MDC 신호선이 존재한다.

데이터버스가 4bit(TXD, RXD)임으로 클럭을 25MHz까지 지원해야 최대 100Mbps 전송이 가능하다.

RMII : Reduced Media Independent Interface

RMII는 MII 인터페이스의 라인을 줄인 형태로, Reduced MII인 것이다.

TXD, RXD 신호선을 각각 2bit 씩 줄여서 사용한다.

데이터버스가 2bit가 되었음으로 클럭을 50MHz까지 지원해야 최대 100Mbps 전송이 가능하다.

GMII : Gigabit Media Independent Interface

GMII는 Gigabit를 지원하는 MII로 1000Mbps 속도를 지원하는 인터페이스이다.

데이터버스는 8bit로 동작하며, 클럭의 속도는 최대 125MHz를 지원한다. (8bit * 125MHz = 1000Mbps)

MAC과 PHY가 8bit 인터페이스가 되어 8B/10B Encoding이 이루어진다.

RGMII : Reduced Gigabit Media Independent Interface

RGMII는 라인선을 줄인 GMII이다.

라인선을 줄였지만 클럭은 최대 125MHz를 지원한다.클럭의 속도가 그대로이니 Gigabit 속도를 지원하기 위해 TXD, RXD를 Double Rate로 사용한다.즉, 클럭의 상승과 하강 에지 모두 사용한다.

SGMII : Serial Gigabit Media Independent Interface

SGMII는 TXD, RXD가 1bit의 diff 신호선을 사용하는 GMII이다.

TX_CLK, RX_CLK도 diff 신호선을 사용한다.

클럭 속도는 625MHz 이며, 데이터비트를 DDR로 사용한다.

SerDes란, Serializer(직렬화)-Deserializer(병렬화)의 약자이다.

SerDes를 통해 제한된 입출력 신호를 보장하기 위해 고속 통신에서 일반적으로 사용되는 기능 블록이다.즉, SerDes 블록은 직렬 데이터와 병렬 인터페이스 사이에서 데이터를 변환시킨다.다시 말해, SerDes는 고속 시리얼 통신을 위해 송신단에서 데이터를 직렬화하고,수신단에서 병렬데이터로 변화하는 기능 블록을 뜻한다.

References

https://dokkodai.tistory.com/176

'Network > Embedded' 카테고리의 다른 글

| 안드로이드 RIL(Radio Interface Layer) 개요 (0) | 2023.07.25 |

|---|---|

| Auto-Nego(Auto-Negotiation) 란? (0) | 2023.04.01 |

| WOL(Wake On Lan) 이란? (0) | 2023.04.01 |